| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- 컴퓨터공학과

- codeit

- CA

- 제품증정 #에스트라 #에스트라퓨처랩서포터즈 #리제덤아이세럼 #더마아이세럼 #레티노이드아이세럼

- 방학

- 맥북FaceID

- 개발

- 컴퓨터구조개념

- 스프링장점

- 나는주니어개발자다

- 책평가

- 코멘토5주인턴

- 개발자

- 소프트웨어

- .env파일

- 백엔드

- 컴퓨터공학

- 함꼐자라기

- 코드잇파이썬

- 스프링부트개발

- computerarchitecture

- 졸업영어

- Python

- 말하기시험

- 코멘토취업

- 컴퓨터구조

- JS

- 파이썬

- 코드잇

- MIPS

- Today

- Total

sollog

[CA] - Basics of cache 본문

- Direct mapped cache operaiton

- Handling cache missed

- Write policy

Cache

- block size is one word of data

"direct mapped " : for each item of data at the lower level, there is exatly one location in the cache where it might be.

캐쉬에 들어갈 자리가 하나고, 정해져있어.

***

Direct Mapped Cache

- Mapping : address is modulo the number of blocks in the cache

- Location in the Cache = (Block address) modulo (Number of Cache Blocks in the Cache)

Cache의 block size는 8이므로, Memory를 8개로 나누어서 각각 mapping 합니다.

이때 1:1 대응 관계에 있으므로, 만약 memory 주소 00001이 cache의 001에 이미 위치하고 있다면,

다른 메모리 정보가 들어가기 위해서는 교체를 해야 합니다.

01101은 13 % 8 = 5이므로, cache의 5번째 block에 mapping 됩니다.

여기서 Valid bit, Tag의 개념 짚고 넘어가기.

이때 하위 비트는 cache의 번지로 지정되어 있으므로, 메모리 주소를 지정하기 위해서는 상위 비트가 추가적으로 필요하다.

이때 상위 비트를 tag라고 부른다.

11001에서 하위 비트는 001, 상위 비트(tag)는 11이 된다.

따라서 cache는 tag 정보도 함께 저장한다.

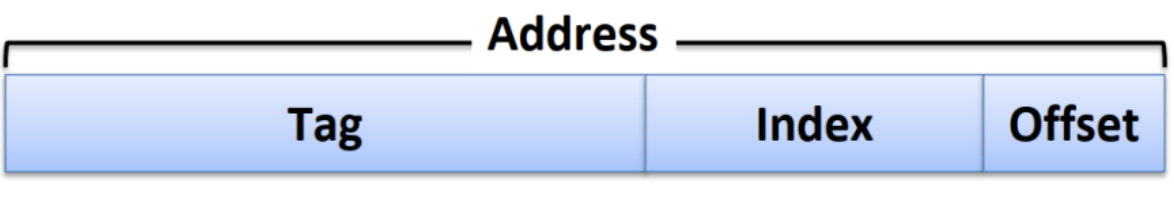

다음은 Tag, Index, Offset을 담고있는 Address의 구조이다.

indrect Mapped Cache Example (MIPS)

Cache has 1024 words -> 10 bits are used as index (location in the cache)

each block is 1 word (4 bytes)

Tag Size : 32 - 10 - 2 = 20bits

1 bit of valid bit

- Cache has 1024 words

-> 10 bits are used as index (location in the cache)

- each block is 1 word (4byte)

- Tag Size : 32 - 10 - 2 = 20 bits

- 1 bit of valid bit

- total number of bits in cache = 1024 * (32 + 20 + 1 )

word * data * data * valid bit

or

으로 표현할 수 있음

***

Hits vs Misses

- Read Hits : this is what we want! // 캐쉬에 있어

- Read Misses : stall the CPU, fetch block from memory, deliver to cache, restart. // 캐쉬에 없어

**The Basic Approach to Cache Miss**

- Stall the CPU, freezing the contents of all the register while waiting for memory

- A seperate controller handles the cache miss, fetching the data into cache from memory

- Once the data is present, Restart the excution

Handling Cache Misses

The instrution and data memory in chap 4 may be replaced by instruction cache and data cache

- Closer Look at the Read Miss

[for instrction cache]

1. Send PC -4 to memory => // 이미 PC+4 가 되서 instructioin cache 인 경우에만!

2. Read blcok from memory, CPU stalls.

3. Write the cache entry (data + tag) and set valid bit on

4.Restart the instruction excution (refetch instruction)

// 2-4 단계는 instrcution cache 와 data cache 의 공통점이다.

- Write through : the information is written to both the block in the main memory.

- Write back : the information is Written only to the block in the cache. The modified cache block is written to main memory only when it is replaced.

정보는 오직 캐시의 블럭에 의해 써진다.

변경된 cache block은 메인 메모리에 써진다.

Dirty : Dirty bit = 1 값이 변했음

=> cache block이 업데이트 된 것

Clean : Dirty Bit = 0 값이 변하지 않았음

=> cache block이 업데이트 되지 않은 것

Miss가 발생하면, memory에서 새로운 걸 가지고 와야해. dirty bit도 변경 필요.

'자기계발 > Study' 카테고리의 다른 글

| [CA] - Hazard (1) | 2023.12.12 |

|---|---|

| [CA] - Improving cache performance (0) | 2023.12.01 |

| [CA] - Memory hierarchy general (0) | 2023.11.30 |

| [CA] - ch4 The Processor (0) | 2023.11.08 |

| 실수를 기회삼아 (0) | 2023.11.05 |